Electronic-photonic integrated circuits based on III-V photonic-wire waveguides

竹中 充 (Mitsuru TAKENAKA, Ph. D.) 東京大学大学院 工学系研究科 電気系工学専攻 准教 授

(Associate Professor, Department of Electrical Engineering and Information Systems, School of Engineering, The University of Tokyo)

IEEE 応用物理学会 電子情報通信学会

受賞:第6回応用物理学会シリコンテクノロジー分科会論文賞 (2014) IEEE EDS Paul Rappaport Award (2014) エレクトロニクスソサイエティ活動功労表彰 (2013) 電子情報通信学会学術奨励賞 (2005) 応用物理学会講演奨励賞 (2003)

研究専門分野:シリコンフォトニクス 光電子集積回路

研究概要 筆者らは、III-V 族化合物半導体版シリコンフォトニクスと呼べる III-V CMOS フォトニクス・プラットフォームを用いた光電子集積回路の研究を進めている。III-V 族半導体の持つ優れた光学物性および電子物性とシリコンフォトニクスの大規模集積性を併せ持つことで、既存の素子を凌駕する光電子集積回路が実現できるものと期待されている。筆者らは、ウェハボンディングを用いた高品位 III-V-on-Insulator(III-V-OI)基板を実現することで、III-V 族半導体細線導波路を用いた種々のパッシブ光素子やアクティブ光素子の研究を進めてきた。本論文では、低暗電流InGaAs 受光器やInGaAsP光変調器/スイッチ、駆動用InGaAs MOSFET とのモノリシック集積などの最近の成果について報告する。

#### 1. はじめに

スマートフォンの普及に伴うクラウドサービスの拡充に加えて、近年のビッグデータ解析、Internet of Things (IoT)、人工知能への期待への高まりも相まって、インターネット通信量は増加の一途を辿り、2025

年~2030年頃に100 Tbps に達するものと予想されている。それに伴い、データセンターの大規模化が今後も進展することが予想される。しかし、データセンターの消費電力が急増していることから、性能向上を実現しつつ省電力化することが急務となっている。データセンター内においては、ラック間通信に光インターコネクションが導入されており、一層の通信容量の拡大と低消費電力動作が求められている。加えて、ラックサイズの制約から、光インターコネクションモジュールの一層の小型化が要求されている。

このような背景のもと、シリコンフォトニクス技術を用いたデータセンター向け光インターコネクション光電子集積回路の研究開発が世界中で活発に進められている。CMOS標準プロセスを用いた大口径シリコンウェハ上に光素子を集積でき、Si-on-insulator (SOI)構造を活かした光閉じ込めの大きな Si 細線導波路による超小型化も可能なことから、種々の小型、大規模パッシブ光素子に加えて、Si 変調器や Ge 受光器との集積化も進められている。IBM や ST マイクロエレクトロニクス・Luxtra 連合、Intel などの半導体大手製造会社が開発したシリコンフォトニクス集積チップが、まさにデータセンター向け光インターコネクションへ導入されつつある。

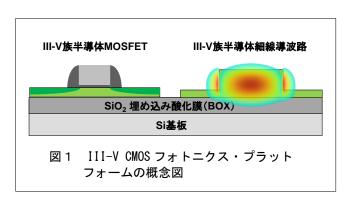

優れた光集積回路プラットフォームを提供可能なシ リコンフォトニクスであるが、間接遷移型半導体であ る Si を用いるため、半導体レーザーや受光器を集積す るためには、III-V族半導体やGeなどの異種半導体を 集積する必要がある。III-V 族半導体層を Si 導波路上 に貼り合わせたハイブリッド型半導体レーザーの研究 が進められているが、光閉じ込めが小さく、閾値電流 が大きいなどの本質的問題を抱えている。また、自由 キャリア効果を用いた光変調器も効率が低く、素子の 小型化や省電力化の障害となっている。このような問 題を解決するために、筆者らは、SOI 基板の Si 層を III-V 族半導体層に置き換えた III-V-on-insulator (III-V-OI) 基板を用いた III-V CMOS フォトニク ス・プラットフォームを提唱し、研究を進めてきた[1]。 図1に、プラットフォームの概念図を示す。Si 基板上 に下部クラッドとなる厚膜 SiO2 埋め込み酸化膜 (Buried Oxide, BOX) を形成し、その上に 200~300

Electronic-photonic integrated circuits based on III-V photonic-wire waveguides

nm 程度の薄層 III-V 層を貼り合わせた構造となって いることで、シリコンフォトニクスと同様の強い光閉 じ込めをもった III-V 族半導体細線導波路デバイスを 作製できる。いわば III-V 族半導体版シリコンフォ トニクスを実現することが可能になる。加えて、直 接遷移半導体であることから、極めて高性能な半導 体レーザーや光変調器、受光器をモノリシック集積 することが出来る。電子移動度も高いことから、論 理回路応用を目指した III-V 族半導体 MOSFET  $(metal\text{-}oxide\text{-}semiconductor\ filed\text{-}effect\text{-}transistor)$ [2]も研究開発が進められており、III-V 族半導体細線 導波路デバイスとの集積化も可能である。筆者らは、 世界に先駆けて高品位 III-V-OI 基板をウェハボンディ ングで実現し[3]、種々の細線導波路パッシブ素子 [3][4]に加えて、光変調器/スイッチ[5]、受光器[6]な どのアクティブ素子を実証してきたので、近年の研究 成果をここに紹介する。

#### 2. 研究成果

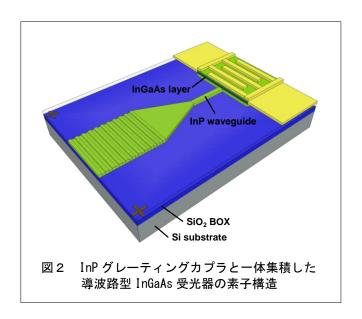

III-V-OI 基板上に低暗電流受光器を作製する研究を進めた。図2に素子構造を示す。InP 細線導波路に導波路型 InGaAs 受光器が接続されている。受光器はショットキー接合を利用した Metal-semiconductor-metal (MSM) 構造となっている。また、光ファイバとの接続を容易にするグレーティングカプラも一体集積した構造となっている。

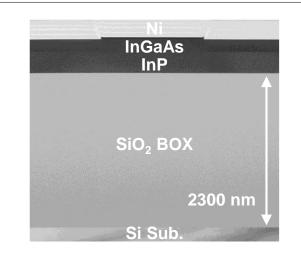

素子作製に先立ち、ウェハボンディングで III-V-OI 基板を作製した[6]。InP 基板上に InP 導波路層および InGaAs 受光層を積層した構造を成長した。一方、Si 基板を熱酸化することで厚膜  $SiO_2$  クラッドを形成した。その後、両基板の表面に極薄膜のアルミナを原子

層堆積法(atomic layer deposition)で堆積した後、 貼り合わし、InP 基板を選択的にウェットエッチング した。図 3 に、素子作製後の III-V-OI 基板の断面 TEM 像を示す。筆者らが開発した低ダメージボンディング 技術により、III-V 層が良好に Si 基板上に貼り合わさ れていることが分かる。

図3 ウェハボンディングで作製した導波路型 InGaAs 受光器用 III-V-0I 基板の断面 TEM 像

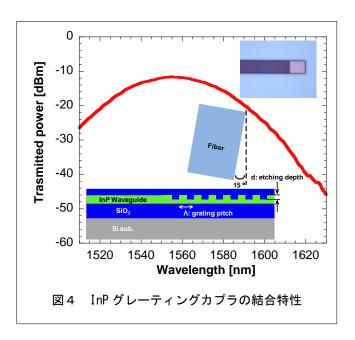

まず、III-V-OI 基板を用いて、受光器と一体集積する InP グレーティングカプラを作製した[7]。InGaAs 層を除去後、電子線描画を用いてグレーティングおよび導波路を形成した。InP 層のエッチングには、メタ

Electronic-photonic integrated circuits based on III-V photonic-wire waveguides

ン/水素混合ガスによるドライエッチングを用いた。 図 4 に、素子断面図、上面写真および光ファイバとの 結合特性結果を示す。入出力はへき開したシングルモード光ファイバである。光ファイバとの結合損失は約 5.5 dB が得られ、ほぼ設計通りの特性が得られた。結 合損失に関しては、グレーティング構造の最適化により、さらに低減可能である。

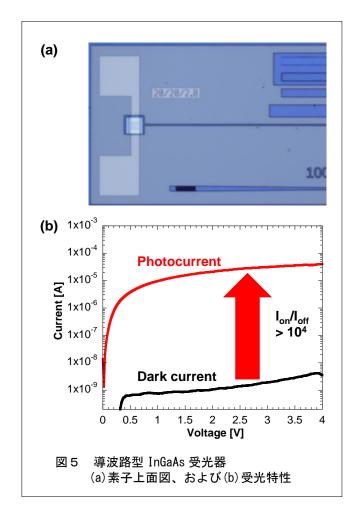

次に、InP グレーティングカプラと一体集積した導波路型 InGaAs 受光器の作製を進めた[7]。図 5a に、作製した素子上面写真を示す。Ni を用いた櫛形電極を用いた MSM 受光器となっている。図 5b に、光電流および暗電流特性を示す。InGaAs 受光層を Ni 電極の間に InAlAs 層を挿入することで、等価的なショットキー障壁を高め、なおかつ、表面リーク電流を低減することで、大幅に暗電流を抑制することに成功した[8]。1V バイアス印加時に暗電流は 0.75 nA であった。受光感度も約 0.2 A/W の値が得られた。今後、InAsAsを組成傾斜構造とすることで、更なる特性向上が期待される。

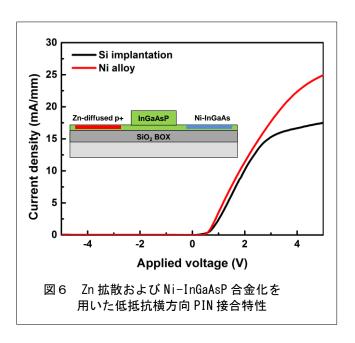

筆者らは、電流注入型光スイッチの研究にも取り組んでいる。導波路に沿って形成した横方向 PIN 接合を用いた電流注入デバイスにおいては、接合の低抵抗化が極めて重要である。研究開始当初は、Si 素子で広く使われているイオン注入法を用いた接合形成の研究を

進めた[5]。接合形成自体は可能であるものの、特に、P型領域の抵抗が高いことが問題であるという認識に至った。この問題を解決するため、筆者らは Zn を添加したスピンオングラスを用いた固相拡散技術の研究を進めた。素子上に塗布したスピンオングラスを 550度に加熱することで、Zn 原子が InGaAsP 中に拡散し、低抵抗 P型領域が形成可能であることを明らかにした。

これにより、大幅な寄生抵抗低減を実現した。筆者らは、更なる寄生抵抗の低減およびプロセス温度の低減を目指し、Si 注入により形成していた N型 InGaAsP層を Ni-InGaAsP合金層に置き換える研究を試みた[9]。InGaAsP上に Ni を堆積し、250度~400度で加熱すると、アロイ化し Ni-InGaAsP合金を形成する。筆者らは、i-InGaAsP層に対して Ni-InGaAsP合金層が良好なオーミック接触特性を示すことを見出した。また、金属である Ni-InGaAsPは、不純物を添加した

Electronic-photonic integrated circuits based on III-V photonic-wire waveguides

N型 InGaAsP 層より低抵抗であることから、N型 InGaAsP を Ni-InGaAsP に置き換えることで、低抵抗 PIN 接合が形成可能であることを明らかにした。図 6 に、スピンオングラスを用いた P型 InGaAsP と Ni-InGaAsP 合金を組み合わせて作製した横方向 PIN接合の電流-電圧特性を示す。Si イオン注入で形成した N型層と比べて寄生抵抗が低減したことから、より大きな電流注入が可能になっていることが分かる。

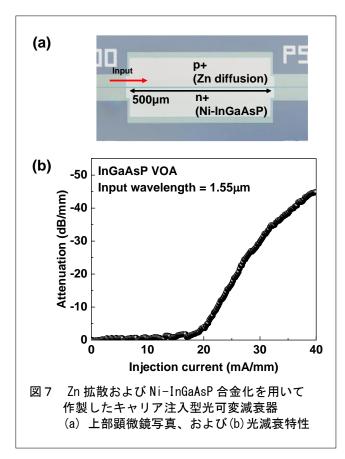

Zn 拡散および Ni-InGaAsP 合金化を用いて、キャリア注入型光可変減衰器 (variable optical attenuator) の作製を試みた[10]。横方向 PIN 接合を通じて電子およびホールを導波路に注入すると、自由キャリアにおり光損失が生じるので、光減衰量を自在に制御可能となる。作製した素子の上部顕微鏡写真を図 7a に示す。電流注入時の波長 1550 nm における光減衰量の測定結果が図 7b となる。接合の低抵抗化により、大きな電流が注入可能となったことから、ホールの価電子帯吸収を用いた動作が実現した。その結果、40 mA/mmの電流中時に45 dB/mmという大きな光可変減衰量を得ることに成功した。

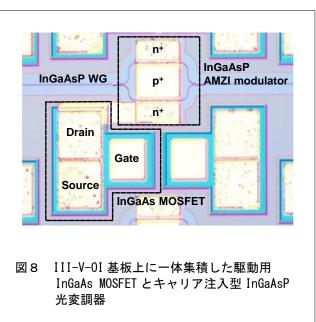

同じ低抵抗 PIN 接合を用いたキャリア注入型光変調器/光スイッチの研究も進めた。キャリア注入による位相変調を用いることで、マッハ・ツェンダー干渉計での光変調動作を実現した。また、図8に示したよ

うに、一体集積した InGaAs MOSFET のオン電流で、 直接キャリア注入型 InGaAsP 光変調器を駆動するこ とにも世界で初めて成功した[11]。

Electronic-photonic integrated circuits based on III-V photonic-wire waveguides

#### 3. まとめ及び将来展望

筆者らは、貼り合わせ III-V-OI 基板を用いて、シリ コンフォトニクスを上回る高性能光電子集積回路が実 現可能な III-V CMOS フォトニクス・プラットフォー ムを開拓してきた。当初、Si と比べて熱的に不安定な III-V 族半導体を貼り合わせた基板上のプロセスは制 約が多く、作製可能な素子も限定されていた。しかし、 研究の進展に伴い耐熱性が向上するとともに、横方向 接合形成技術や再成長技術が確立しつつあり、低閾値 半導体レーザー[12]も報告されるようになっている。 半導体レーザー、光変調器、受光器などの要素アクテ ィブ素子が揃いつつあり、今後は大規模集積化への展 開が期待される。パッシブ素子においては、Si 導波路 並みの損失低減は実現できていないが、低損失化に本 質的な問題ないと考えられるので、着実な研究開発を 進むことを期待したい。また、InGaAs MOSFET を使 った駆動用回路のモノリシック集積への道筋も示され た。電子移動が高い InGaAs を使うことで高周波動作 が可能であり、高速動作する光素子の駆動用トランジ スタに適していると言える。最先端 Si CMOS プロセ スとの不整合から、近年は電子回路をシリコンフォト ニクスチップ上にフリップチップ実装する手法が用い られている。しかし、より高周波動作になると光素子 近傍に高速駆動回路をモノリシック集積する方法が優 れていると期待される。このように、III-V CMOS フ オトニクス・プラットフォームは、シリコンフォトニ クス技術を吸収しつつ、より優れた光電子集積回路を 実現可能であり、今後も大きく進展行くことを期待し たい。

#### 謝辞

本研究は、文科省科研費補助金若手研究 A および一般財団法人テレコム先端技術研究支援センターの助成により実施した。

#### 参考文献

[1] M. Takenaka and Y. Nakano, "InP photonic wire waveguide using InAlAs oxide cladding layer," *Opt. Express*, vol. 15, no. 13, pp. 8422–8427, 2007.

- [2] S.-H. Kim, M. Yokoyama, R. Nakane, O. Ichikawa, T. Osada, M. Hata, M. Takenaka, and Shinichi Takagi, "High performance tri-gate extremely thin-body InAs-on-insulator MOSFETs with high short channel effect immunity and V<sub>th</sub> tunability," *IEEE Trans. Electron Devices*, vol. 61, no. 5, pp. 1354 1360, 2014.

- [3] M. Takenaka, M. Yokoyama, M. Sugiyama, Y. Nakano, and S. Takagi, "InGaAsP photonic wire based ultrasmall arrayed waveguide grating multiplexer on Si wafer," *Appl. Phys. Express.*, Vol. 2, 122201, 2009.

- [4] M. Takenaka, M. Yokoyama, M. Sugiyama, Y. Nakano, and S. Takagi, "InGaAsP grating couplers fabricated using complementary-metal-oxide-semiconductor-com patible III-V-on-Insulator on Si," Appl. Phys. Express., Vol. 6, 042501, 2013.

- [5] Y. Ikku, M. Yokoyama, O. Ichikawa, M. Hata, M. Takenaka, and S. Takagi, "Low-driving-current InGaAsP photonic-wire optical switches using III-V CMOS photonics platform," *Optics Express Letters*, vol. 20, no. 26, pp. B357-B364, 2012.

- [6] Y. Cheng, Y. Ikku, M. Takenaka, and S. Takagi, "InGaAs MSM photodetector monolithically integrated with InP photonic-wire waveguide on III-V CMOS photonics platform", *IEICE Electronics Express*, vol. 11, no. 16, pp. 20140609, 2014.

- [7] Y. Cheng, Y. Ikku, M. Takenaka, and S. Takagi, "Low-dark-current waveguide InGaAs metal-semiconductor-metal photodetector monolithically integrated with InP grating coupler on III-V CMOS photonics platform," *Jpn. J. Appl. Phys.*, Vol. 55, 04EH01, 2016.

Electronic-photonic integrated circuits based on III-V photonic-wire waveguides

- [8] Y. Cheng, Y. Ikku, M. Takenaka, and S. Takagi, "Surface leakage reduction in MSM InGaAs photodetector on III–V CMOS photonics platform," *IEEE Photonics Technology Letters*, Vol. 27, No. 14, pp. 1569-1572, 2015.

- [9] J.-K. Park, M. Takenaka, and S. Takagi, "Low resistivity lateral P-I-N junction formed by Ni-InGaAsP alloy for carrier injection InGaAsP photonic devices," *Jpn. J. Appl. Phys.*, Vol. 55, 04EH04, 2016.

- [10] J.-K. Park, J. Han, M. Takenaka, and S. Takagi, "InGaAsP variable optical attenuator with lateral P-I-N junction formed by Ni-InGaAsP and Zn diffusion on III-V on insulator wafer," MRS Advances, vol.1 no. 48, pp. 3295-3300, 2016.

- [11] J.-K. Park, S. Takagi, and M. Takenaka, "Monolithic Integration of InGaAsP MZI Modulator and InGaAs Driver MOSFET using III-V CMOS Photonics," Optical Fiber Communication Conference (OFC2017), Los Angeles, March 2017.

- [12] S. Matsuo, T. Fujii, K. Hasebe, K. Takeda, T. Sato, and T. Kakitsuka, "Directly modulated buried heterostructure DFB laser on SiO<sub>2</sub>/Si substrate fabricated by regrowth of InP using bonded active layer," *Opt. Express*, vol. 22, no. 10, pp. 12139–12147, 2014.

この研究は、平成24年度SCAT研究助成の対象として採用され、平成25~27年度に実施されたものです。