Brain-type Integrated System using Analog Cellular Neural Network

木村 睦 ( Mutsumi Kimura, Ph. D.(Eng.), Ph.D.(Sci.)) 龍谷大学 先端理工学部 教授

(Professor, Ryukoku University, Faculty of Advanced Science and Technology)

電子情報通信学会 応用物理学会 Institute of Electrical and Electronics Engineers (IEEE) Society for Information Display (SID)

受賞: Best of the International Conference on Display Technology (ICDT) 2019 (2019年) APEX / JJAP Editorial Contribution Award (2019年) ベストペーパーアワード, 薄膜材料デバイス研究会 第 15 回研究集会 (2018年) 日本熱電学会 学術講演会 優秀講演賞 (2018年) 平成27年 電子・情報・システム部門 技術委員会奨励賞 (2015年) 他

著書: High Quality Liquid Crystal Displays and Smart Devices, Thin Film Transistors for Active Matrix LCDs, The Institution of Engineering and Technology (IET) (2019 年) スッキリ!がってん! 有機 EL の本,電気書院 (2016 年), 搭載!! 人工知能,電気書院 (2016 年) 半導体デバイス工学,金属と半導体の接合,バイポーラトランジスタの動作原理, 薄膜トランジスタ,オーム社 (2008 年) 薄膜トランジスタ, TFT の動作原理, コロナ社 (2008 年) 他

研究専門分野:電子デバイス工学 ニューロモーフィックシステム 人工 知能

### あらまし

本研究は、将来的にコンパクト・ロバスト・超低消費 電力なポストノイマン型人工知能を目指し、デバイス レベルから生体の神経回路の構造・動作・機能を再現 する、アナログセルラニューラルネットワークを用い た脳型集積システムの研究開発を行う。本研究では、 薄膜可変抵抗素子・メモリスタを開発し、シナプス素 子としての動作を確認し、脳型集積システムの実用性 を検証するため、文字認識や画像認識への応用可能性 を評価することを目的としている。まず、ニューロン LSIは、チップを試作し、ニューロンとしての正常な 動作を確認した。薄膜シナプスは、可変抵抗素子とし て、一定の電圧を加えて電流を流すことにより、徐々 にコンダクタンスが低下することを確認した。次に、 メモリスタの開発として、繰返特性としては、徐々に オンオフ比は小さくなるものの、100万回のオンオフ 動作ののちでもメモリスタ特性が維持されること、お よび、保持特性としては、1000 時間の特性維持ができることがわかった。さらに、ミスト CVD 法を用いたメモリスタの動作の確認に成功した。最後に、積層構造の薄膜可変抵抗素子をニューロン LSI のうえに作成したアナログセルラニューラルネットワークで、アルファベットの連想記憶の動作確認に成功した。

### 1. 研究の背景と目的

人工知能は、未来社会の全分野の中核技術として期待されている。しかし、現在の人工知能は、超大規模で超高速のノイマン型コンピュータの集合体である多くのサーバーに、ネットワークを経由して接続され、それらサーバー上のソフトウェアとして動作している。そのため、表1に示すように、サイズ、非ロバスト性、電力という課題がある。

表 1. 我々が目指す脳型集積システムと現在の人工知能との比較

| 我々が目指す脳型集積システム                                                                                                                                    | 項目    | 現在の人工知能                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------|

| デバイスレベルからの生体神経回路の再現                                                                                                                               | 構成    | ノイマン型コンピュータ上の<br>ソフトウェアとして動作 |

| 並列分散処理                                                                                                                                            | 動作    | 順次動作                         |

| 低い                                                                                                                                                | 汎用性   | 高い                           |

| ・ニューロン/シナプス = 10 <sup>9</sup> 個 / 10 <sup>10</sup> 個で 1 cm <sup>3</sup><br>・ニューロン/シナプス = 10 <sup>12</sup> 個/10 <sup>13</sup> 個で10 cm <sup>3</sup> | 大きさ   | 部屋サイズ                        |

| 個々の「モノ」に搭載                                                                                                                                        | 使用方法  | ネットワーク経由                     |

| 強い (通信に影響されない)                                                                                                                                    | ロバスト性 | 弱い (通信状態に影響)                 |

| ・ニューロン/シナプス = 10 <sup>9</sup> 個/10 <sup>10</sup> 個で 1 W以下<br>・ニューロン/シナプス = 10 <sup>12</sup> 個/10 <sup>13</sup> 個で100W以下                           | 消費電力  | 200kW                        |

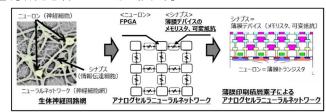

そこで我々は、このような人工知能の課題の解決策として、デバイスレベルから本質的に生体の神経回路の構造・動作・機能を再現する、アナログセルラニューラルネットワーク\*1を用いた脳型集積システム\*2の基礎研究を行っている(図 1)。

図 1. 我々が目指すアナログセルラニューラルネットワークを用いた 脳型集積システム

我々の研究は、超大規模集積化が可能な薄膜デバイスの積層構造で3次元LSIを作製するので、サイズが革命的にコンパクトになることが最大の特徴である。また、脳型集積システムでは、全体に機能が分散され

Brain-type Integrated System using Analog Cellular Neural Network

るため、一部の素子の不良に対しても一定の動作が保証され、ロバスト性は強固なものとなる。さらに、並列分散処理で個々のデバイスの動作速度を抑制できるとともに、非同期型でクロック信号がないため、圧倒的に低消費電力となる。すなわち、表1に示すようなコンパクト・ロバスト・低消費電力の人工知能を実現することが最終の研究目標である。一方、このような脳型集積システムは、ハードウェアの段階で人工知能に必要な基本的な機能を有しているため、ソフトウェアは最小限で対応でき、かつ、ハードウェアはきわめてコンパクトにできるので、個々の「モノ」、例えば IoTセンサに独立した人工知能を搭載できることにもなる。

この研究では、まず、脳型集積システムの基礎研究として、薄膜デバイスのメモリスタ\*3 および可変抵抗素子を開発し、セルラニューラルネットワークのシナプス素子としての動作を確認する。そして、この脳型集積システムの実用性を検証するため、文字認識や画像認識への応用可能性を評価する。

### 2. 研究の特徴

ニューラルネットワークは、多数のニューロンが多数のシナプスで接続されており、シナプスの伝達効率が変化することが、記憶や学習に重要な役割を持つと考えられている。我々の研究は、これらシナプスとニューロンの実現方法含め、以下の3点の特徴がある。(1)シナプスを1個の素子で構成

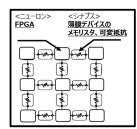

TFTの制御電圧をコントロールすることで、半導体デバイスにおけるホットキャリアやジュール熱という現象によるTFTの特性変化を積極的に誘起させ、これをシナプスの結合強度の変化に利用する方式は、試作と動作確認を終えている。本研究では、学習による特性変動の安定化効果と低消費電力化を実現するメモリスタによるシナプスの実現を行う(図 2)。

図 2. 本研究のアナログセルラニューラルネットワーク構成

(2) 反転回路 2 個による超簡略化ニューロン構成

ニューラルネットワークの学習則としては、シナプスの結合強度が、その両端のニューロンが同時に活性化するときに強化されるという Hebb 学習則が知られている。我々は、ニューロンの構成を簡略化するために、シナプスの結合強度が、両端のニューロンの状態が異なるときに弱化されるという修正 Hebb 学習則を考案することで、ニューロンの構成を超簡略化した。(3)薄膜デバイスが有する 3 次元積層構造やプリンテッドプロセスへの適合性よる超集積化や低コスト化への可能性

脳型集積システムを超大規模集積化するためには、 多層でかつ低コストの3次元化技術が必須であるが、 現在進められているLSIの3次元化技術は、この要 求を満たせない。しかし、薄膜デバイスは、低温作製 可能・高材料使用効率などの長所があり、デバイスの 大面積化や3次元積層化に適している。特に、プリン テッド(印刷)プロセスの研究開発は、多数の国家・ 公的なプロジェクトや組織があり、日本が誇れる技術 の一つである。

### 3. 研究の方法

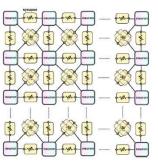

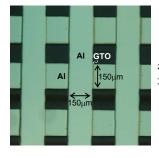

まず、ニューロンとして、反転回路2個まで簡略化 したマトリクス状の 25×25 個または 32×32 個のニュー ロンを備えた LSI を設計・試作した。いっぽう、シナ プスとして、低温作製・印刷プロセス・3次元積層・ 低コスト化などが期待でき最近注目を集めているアモ ルファス金属酸化物半導体 (AOS) の一種である Ga-Sn-0 (GTO) 薄膜を、ここではスパッタで作製し、可変抵 抗素子としての特性を評価した。同時に、デバイス構 造や製造プロセスを最適化することで、メモリスタと しての特性も評価した。そして、ニューロン LSI のう えに GTO 薄膜シナプスを積層した。これは、我々の提 唱するニューラルネットワークアーキテクチャと修正 Hebb 学習則により、アナログセルラニューラルネット ワークとして動作することが期待できる。このアナロ グセルラニューラルネットワークで、複数の文字を学 習し、一部が歪んだ文字を入力すると補正した文字を 出力するかどうか、すなわち、文字認識の機能を確認

Brain-type Integrated System using Analog Cellular Neural Network

した。

つぎに、薄膜可変抵抗素子の開発として、In-Ga-Zn-0 (IGZO) と Ga-Sn-0 (GTO) に関して、別途でシミュレ ーションで得られている指針のとおり、初期特性のバ ラツキを一定範囲に抑制し、変化特性を数十%とし、 変化特性のバラツキも一定範囲に抑制することを試み た。次に、メモリスタの開発として、繰返特性と保持 特性の改善を試みた。同時に、より動作を確実にする ために、あらたな構造を提案した。これらの薄膜可変 抵抗素子とメモリスタは、我々の提案する修正へブ学 習則を適用することで、脳型集積システムにおけるシ ナプス素子として使用することが可能となるはずであ る。そこで、シナプス素子としての動作を確認し、脳 型集積システムの実用性を検証するため、ニューロン LSI のうえに、IGZO や GTO の薄膜シナプスを積層した アナログセルラニューラルネットワークを作成した。 この、アナログセルラニューラルネットワークを用い て、文字認識の動作確認を試みた。

そして、薄膜可変抵抗素子の開発として、低温薄膜 プロセスや印刷プロセスによる3次元積層化で高度集 積化の可能性が期待できるアモルファス酸化物半導体 に関して、これまでの知見を活かしつつ、初期特性と 抵抗変化の均一性を向上させるため、成膜時の製造プ ロセス条件の異なる積層構造の試作と評価を試みた。 次に、メモリスタの開発として、引き続いて、やはり、 成膜時の製造プロセス条件の異なる積層構造の試作と 評価を試みた。さらに、ミスト CVD 法という印刷プロ セスのひとつを用いたメモリスタの試作と評価を試み た。これは、より3次元積層化の実現に近づくもので ある。これらの薄膜可変抵抗素子とメモリスタは、我々 の提案する局所自律学習則を適用することで、脳型集 積システムにおけるシナプス素子として使用すること が可能となる。そこで最後に、上記のうち、積層構造 の薄膜可変抵抗素子をニューロン LSI のうえに作成し、 アナログセルラニューラルネットワークを構成し、文 字認識の動作確認を試みた。

#### 4. 研究の結果

まず、ニューロンLSIは、異なる4種類の設計で、 80個のチップを試作し、ニューロンとしての正常な動 作を確認した(図3)[1]。

図 3. ニューロン LSI の設計と試作

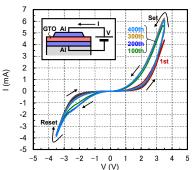

いっぽう、GTO 薄膜シナプスは、可変抵抗素子として、一定の電圧を加えて電流を流すことにより、徐々にコンダクタンスが低下することを確認した[2]。これは、修正 Hebb 学習則を適用可能なシナプスに必要とされる特性である。同時に、上下電極をアルミにすることで、低抵抗状態と高抵抗状態を多数回にわたり遷移する、メモリスタとしての特性が得られることがわかった(図 4)[3]。

図 4. GTO 薄膜デバイスのメモリスタ特性

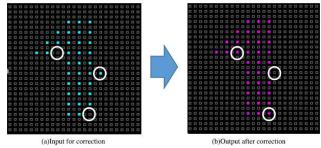

そして、ニューロン LSI のうえに GTO 薄膜シナプス を積層したアナログセルラニューラルネットワークで、部分的に文字認識の機能を得ることに成功した[4]。ここで部分的にしか成功していないのは、本質的な課題ではなく評価の時間が足りないからである。

つぎに、薄膜可変抵抗素子の開発として、成膜条件とくに成膜時の酸素分圧をコントロールすることで、変化特性を所望の値に制御できることがわかった。また、はじめに LED 光を照射することで、初期特性と変化特性のバラツキを一定範囲に制御できることもわか

Brain-type Integrated System using Analog Cellular Neural Network

った。次に、メモリスタの開発として、繰返特性としては、徐々にオンオフ比は小さくなるものの、100万回のオンオフ動作ののちでもメモリスタ特性が維持されること、および、保持特性としては、1000時間の特性維持ができることがわかった。さらに、あらたな構造として、成膜の途中で酸素分圧を変化させることで、膜中の酸素濃度の異なるアモルファス酸化物半導体薄膜の積層構造で、より動作を確実にすることができた[5]。そして、アナログセルラニューラルネットワークを用いての文字認識の動作確認では、TやLといった簡単なアルファベットの連想記憶の動作確認に成功した。

そして、薄膜可変抵抗素子の開発として、スパッタ 成膜時の酸素とアルゴンの分圧の異なる2層または3 層の積層構造で、初期特性と抵抗変化の均一性を向上 させることに成功した。これは、外部環境からの酸素 や水分の侵入を阻止しつつ、内部条件で素子特性を制 御していることによる。次に、メモリスタの開発とし て、やはり、スパッタ成膜時の酸素とアルゴンの分圧 の異なる2層の積層構造で、フォーミング処理なしに はじめから実動作が可能なメモリスタの開発に成功し た[6]。これは、アナログセルラニューラルネットワー クへの実装に適している。さらに、ミスト CVD 法を用 いたメモリスタの動作の確認に成功した[7]。最後に、 積層構造の薄膜可変抵抗素子をニューロン LSI のうえ に作成したアナログセルラニューラルネットワークで、 アルファベットの連想記憶の動作確認に成功した(図 5) [8]

図 5. アルファベットの連想記憶の動作確認

シミュレーションによればこれまでよりも認識率が 向上することが期待できる。また、これらの結果を、 ニューラルネットワークのトップカンファレンスであ る ICONIP などで講演するとともに[1,2,4,6]、学術雑誌 で発表した[3,5,7,8]。

#### 5. 将来展望

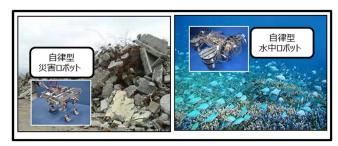

脳型集積システムの3次元積層構造のLSIを作製することで、コンパクト・ロバスト・低消費電力かつstand-alone動作する人工知能の実現に近づくことができる。これにより、自律した人工知能の「モノ」への搭載が可能となり、IoTや IoE のさらなる進展、すなわち、モノのインテリジェント化に貢献できる(表2)。また、より高度なシステムとして、自律型人工知能を実現することで、通信が不安定な瓦礫内の要救援者の探索を行う自律型災害ロボットや、高速通信ができない水中における資源調査を行う自律型水中ロボットの提供も可能となる(図6)。

図 6. 自律型人工知能搭載の災害/水中ロボット

さらに、現在の人工知能の延長では、そのための消費電力は 2025 年には全発電量の 20%で、2050 年には 60%にもなると試算されており、人工知能の普及に致命的な制約となる。低消費電力の脳型集積システムは、社会的なエネルギー消費の観点からも意義あるものである。

### おわりに

本研究は、将来的にコンパクト・ロバスト・超低消費電力なポストノイマン型人工知能を目指し、デバイスレベルから生体の神経回路の構造・動作・機能を再現する、アナログセルラニューラルネットワークを用いた脳型集積システムの研究開発を行った。本研究では、薄膜可変抵抗素子・メモリスタを開発し、シナプス素子としての動作を確認し、脳型集積システムの実用性を検証するため、文字認識や画像認識への応用可能性

Brain-type Integrated System using Analog Cellular Neural Network

を評価することを目的としている。まず、ニューロン LSI は、チップを試作し、ニューロンとしての正常な動作を確認した。薄膜シナプスは、可変抵抗素子として、一定の電圧を加えて電流を流すことにより、徐々にコンダクタンスが低下することを確認した。次に、メモリスタの開発として、繰返特性としては、徐々にオンオフ比は小さくなるものの、100万回のオンオフ動作ののちでもメモリスタ特性が維持されること、および、保持特性としては、1000時間の特性維持ができることがわかった。さらに、ミスト CVD 法を用いたメモリスタの動作の確認に成功した。最後に、積層構造の薄膜可変抵抗素子をニューロン LSI のうえに作成したアナログセルラニューラルネットワークで、アルファベットの連想記憶の動作確認に成功した。

#### 用語解説

\*1 セルラニューラルネットワーク:隣接するニューロンのみが接続するニューラルネットワークで、電子デバイスの集積化に適している。

本研究にあたっては、龍谷大学 龍谷エクステンション

センターの田村光夫氏に感謝する。

- \*2 脳型集積システム:脳の構造をハードウェアのレベルから模倣した集積システム

- \*3 メモリスタ:電圧や電流の印加の履歴に依存するコンダクタンスをもつ回路素子

### 参考文献

- [1] Tomoya Kameda, Mutsumi Kimura, and Yasuhiko Nakashima, Neuromorphic Hardware using Simplified Elements and Thin-Film Semiconductor Devices as Synapse Elements Simulation of Hopfield and Cellular Neural Network -, The 24th International Conference on Neural Information Processing, ICONIP 2017, Pt. VI, LNCS 10639, pp. 769–776, Nov. 2017

- [2] Mutsumi Kimura, Kenta Umeda, Keisuke Ikushima, Toshimasa Hori, Ryo Tanaka, Tokiyoshi Matsuda, Tomoya Kameda, and Yasuhiko Nakashima, Hopfield Neural Network with Double-layer Amorphous Metal-Oxide

- Semiconductor Thin-Film Devices as Crosspointtype Synapse Elements and Working Confirmation of Letter Recognition, The 25th International Conference on Neural Information Processing, ICONIP 2018, Pt. VII, LNCS 11307, pp. 637-646, Dec. 2018

- [3] Sumio Sugisaki, Tokiyoshi Matsuda, Mutsunori Uenuma, Toshihide Nabatame, Yasuhiko Nakashima, Takahito Imai, Yusaku Magari, Daichi Koretomo, Mamoru Furuta, and Mutsumi Kimura, Memristive Characteristic of an Amorphous Ga-Sn-O Thin-Film Device, Scientific Reports, Vol. 9, 2757, Feb. 2019

- [4] Mutsumi Kimura, Keisuke Ikushima, Daiki Yamakawa, Hiroki Yamane, and Yasuhiko Nakashima, Real Neuromorphic System using LSI Chip and Thin-Film Devices, ICONS 2019, July 2019

- [5] Ayata Kurasaki, Ryo Tanaka, Sumio Sugisaki, Tokiyoshi Matsuda, Daichi Koretomo, Yusaku Magari, Mamoru Furuta, and Mutsumi Kimura, Memristive Characteristic of an Amorphous Ga-Sn-O Thin-Film Device with Double Layers of Different Oxygen Density, Materials, Vol. 12, Issue 19, 3236, Oct. 2019

- [6] Mutsumi Kimura, Kenta Umeda, Keisuke Ikushima, Toshimasa Hori, Ryo Tanaka, Tokiyoshi Matsuda, Tomoya Kameda, and Yasuhiko Nakashima, Neuro-inspired System with Crossbar Array of Amorphous Metal-Oxide-Semiconductor Thin-Film Devices as Self-Plastic Synapse Units Letter Recognition of Five Alphabets –, The 26th International Conference on Neural Information Processing, ICONIP 2019, Pt. II, LNCS 11954, pp. 481-491, Dec. 2019

- [7] Yuta Takishita, Masaki Kobayashi, Kazuki Hattori, Tokiyoshi Matsuda, Sumio Sugisaki, Yasuhiko Nakashima, and Mutsumi Kimura, Memristor Property of an Amorphous Sn-Ga-O Thin-Film Device deposited using Mist

Brain-type Integrated System using Analog Cellular Neural Network

Chemical-Vapor-Deposition Method, AIP Advances, Vol. 10, Issue 3, 035112, Mar. 2020

[8] Hiroya Ikeda, Hiroki Yamane, Yuta Takishita, Mutsumi Kimura, and Yasuhiko Nakashima, Influence of Characteristic Variation of Oxide Semiconductor and Comparison of the Activation Function in Neuromorphic Hardware, NOLTA IEICE, Vol. 11, No.2, pp. 232-252, Apr. 2020

この研究は、平成28年度SCAT研究助成の対象として採用され、平成29~令和元年度に実施されたものです。